三維集成與系統(tǒng)級(jí)封裝 集成電路技術(shù)創(chuàng)新的關(guān)鍵路徑——以清華大學(xué)蔡堅(jiān)教授的研究為例

近年來,隨著信息技術(shù)的高速發(fā)展,集成電路技術(shù)不斷向更高集成度、更優(yōu)性能的方向演進(jìn)。在這一過程中,系統(tǒng)級(jí)封裝(System-in-Package, SiP)與三維集成技術(shù)已成為推動(dòng)集成電路技術(shù)發(fā)展的重要?jiǎng)?chuàng)新方向,并在信息系統(tǒng)集成服務(wù)中發(fā)揮著日益關(guān)鍵的作用。清華大學(xué)蔡堅(jiān)教授及其團(tuán)隊(duì)在這一領(lǐng)域的研究,為推動(dòng)我國集成電路技術(shù)的進(jìn)步提供了重要支撐。

系統(tǒng)級(jí)封裝是一種將多個(gè)具有不同功能的芯片、無源元件及其他組件集成于單個(gè)封裝體內(nèi)的技術(shù)。通過系統(tǒng)級(jí)封裝,不僅可以大幅縮小電子設(shè)備的體積與重量,還能提升系統(tǒng)的整體性能與可靠性。與傳統(tǒng)的單芯片封裝相比,系統(tǒng)級(jí)封裝能夠?qū)崿F(xiàn)更復(fù)雜的系統(tǒng)功能,并有效降低功耗與信號(hào)延遲,尤其適用于移動(dòng)通信、物聯(lián)網(wǎng)、人工智能等對(duì)小型化、高性能要求極高的應(yīng)用場景。

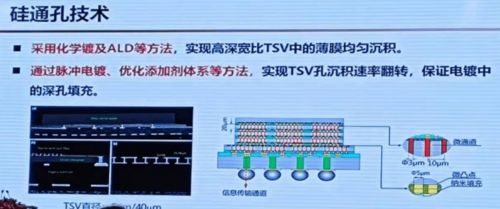

三維集成技術(shù)是系統(tǒng)級(jí)封裝的重要支撐技術(shù)之一。它通過在垂直方向上堆疊多層芯片或晶圓,并使用硅通孔(Through-Silicon Via, TSV)等互連技術(shù)實(shí)現(xiàn)層間的高密度連接,從而突破傳統(tǒng)二維平面集成的物理限制。三維集成不僅能夠顯著提升芯片的集成密度,還能縮短互連長度,降低信號(hào)傳輸延遲與功耗,同時(shí)支持異構(gòu)集成,將不同工藝節(jié)點(diǎn)、不同功能的芯片高效融合。

在信息系統(tǒng)集成服務(wù)中,系統(tǒng)級(jí)封裝與三維集成技術(shù)的應(yīng)用正變得日益廣泛。例如,在高端服務(wù)器、數(shù)據(jù)中心、5G通信基站及智能終端設(shè)備中,這些技術(shù)能夠幫助實(shí)現(xiàn)更高效的數(shù)據(jù)處理與傳輸,提升系統(tǒng)的整體性能與能效。同時(shí),它們也為新興技術(shù)如邊緣計(jì)算、自動(dòng)駕駛和醫(yī)療電子提供了關(guān)鍵的技術(shù)支撐。

清華大學(xué)微電子學(xué)研究所的蔡堅(jiān)教授長期致力于系統(tǒng)級(jí)封裝與三維集成技術(shù)的研究,其團(tuán)隊(duì)在封裝材料、工藝優(yōu)化及可靠性分析等方面取得了多項(xiàng)重要成果。蔡堅(jiān)教授指出,系統(tǒng)級(jí)封裝與三維集成不僅是當(dāng)前技術(shù)發(fā)展的熱點(diǎn),更是未來集成電路技術(shù)持續(xù)創(chuàng)新的核心方向。通過跨學(xué)科合作與產(chǎn)學(xué)研結(jié)合,推動(dòng)這些關(guān)鍵技術(shù)的突破,將為我國集成電路產(chǎn)業(yè)的自主發(fā)展注入強(qiáng)勁動(dòng)力。

隨著人工智能、物聯(lián)網(wǎng)、量子計(jì)算等前沿技術(shù)的快速發(fā)展,對(duì)集成電路的性能、功耗和集成度提出了更高要求。系統(tǒng)級(jí)封裝與三維集成技術(shù)將繼續(xù)在信息系統(tǒng)集成服務(wù)中扮演重要角色,并通過不斷創(chuàng)新,助力全球集成電路技術(shù)邁向新的高度。

如若轉(zhuǎn)載,請注明出處:http://m.hongshantang.cn/product/9.html

更新時(shí)間:2026-02-24 19:59:23